- 您现在的位置:买卖IC网 > Sheet目录2008 > MAX11647EUA+T (Maxim Integrated Products)IC ADC 10BIT I2C 94.4KSPS 8UMAX

MAX11646/MAX11647

Low-Power, 1-/2-Channel, I2C, 10-Bit ADCs

in Ultra-Tiny 1.9mm x 2.2mm Package

14

______________________________________________________________________________________

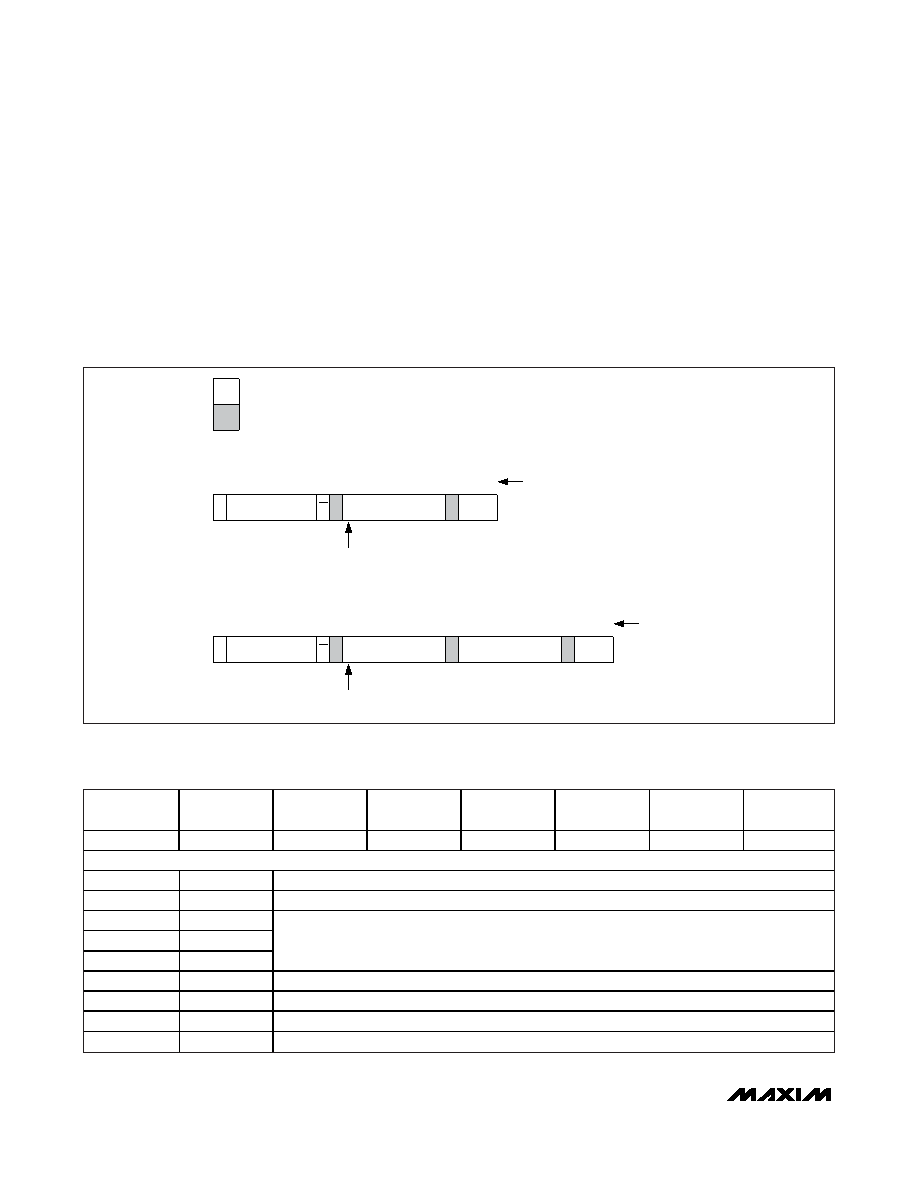

Configuration/Setup Bytes (Write Cycle)

A write cycle begins with the bus master issuing a

START condition followed by 7 address bits (Figure 7)

and a write bit (R/W = 0). If the address byte is success-

fully received, the MAX11646/MAX11647 (slave) issue

an acknowledge. The master then writes to the slave.

The slave recognizes the received byte as the setup

byte (Table 1) if the most significant bit (MSB) is 1. If the

MSB is 0, the slave recognizes that byte as the configu-

ration byte (Table 2). The master can write either 1 or 2

bytes to the slave in any order (setup byte then configu-

ration byte, configuration byte then setup byte, setup

byte or configuration byte only; see Figure 9). If the

slave receives a byte successfully, it issues an acknowl-

edge. The master ends the write cycle by issuing a

STOP condition or a repeated START condition. When

operating in HS mode, a STOP condition returns the bus

into F/S mode (see the

HS Mode section).

B. 2-BYTE WRITE CYCLE

SLAVE TO MASTER

MASTER TO SLAVE

S

1

SLAVE ADDRESS

A

71 1

W

SETUP OR

CONFIGURATION BYTE

SETUP OR

CONFIGURATION BYTE

8

P or Sr

1

A

1

MSB DETERMINES WHETHER

SETUP OR CONFIGURATION BYTE

S

1

SLAVE ADDRESS

A

71 1

W

SETUP OR

CONFIGURATION BYTE

8

P or Sr

1

A

1

MSB DETERMINES WHETHER

SETUP OR CONFIGURATION BYTE

A

1

8

A. 1-BYTE WRITE CYCLE

NUMBER OF BITS

Figure 9. Write Cycle

BIT 7

(MSB)

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

(LSB)

REG

SEL2

SEL1

SEL0

CLK

BIP/UNI

RST

X

BIT

NAME

DESCRIPTION

7

REG

Register bit. 1 = setup byte, 0 = configuration byte (see Table 2).

6

SEL2

5

SEL1

4

SEL0

Three bits select the reference voltage (Table 6). Default to 000 at power-up.

3

CLK

1 = external clock, 0 = internal clock. Defaulted to 0 at power-up.

2

BIP/UNI

1 = bipolar, 0 = unipolar. Defaulted to 0 at power-up (see the Unipolar/Bipolar section).

1

RST

1 = no action, 0 = resets the configuration register to default. Setup register remains unchanged.

0

X

Don’t-care bit. This bit can be set to 1 or 0.

Table 1. Setup Byte Format

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX1166BEUP+

IC ADC 16BIT 165KSPS 20-TSSOP

MAX1168BCEG+

IC ADC 16BIT 200KSPS 24-QSOP

MAX1183ECM+TD

IC ADC 10BIT 40MSPS DL 48-TQFP

MAX1184ECM+TD

IC ADC 10BIT 20MSPS DL 48-TQFP

MAX1186ECM+TD

IC ADC 10BIT 40MSPS DL 48-TQFP

MAX1187CCUI+

IC ADC 16BIT 135KSPS 28-TSSOP

MAX118EAI+

IC ADC 8BIT 1MSPS 28-SSOP

MAX1191ETI+T

IC ADC 8BIT 7.5MSPS DL 28-TQFN

相关代理商/技术参数

MAX11647EWC+T

功能描述:模数转换器 - ADC 12-Bit 2Ch 94.4ksps 3.6V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1165

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Low-Power, 16-Bit Analog-to-Digital Converters with Parallel Interface

MAX1165ACUI

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1165ACUI+

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1165ACUI+T

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1165ACUI-T

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1165AEUI

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1165AEUI+

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32